How To Program A Lattice Cpld Programming

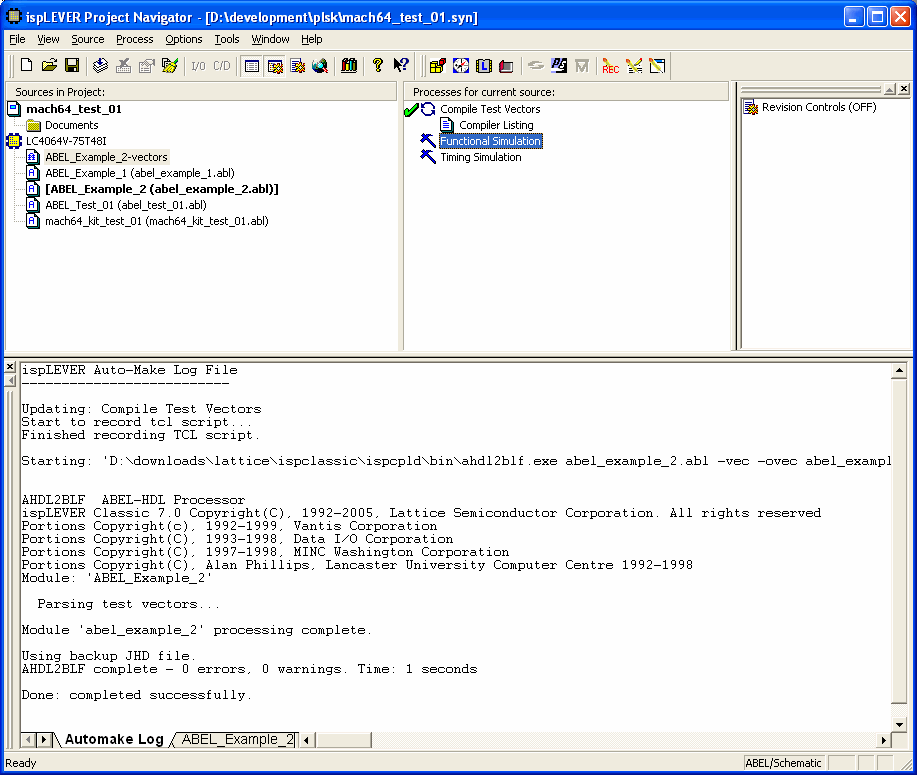

Lattice_GAL_16V8.jpg' alt='How To Program A Lattice Cpld Programming' title='How To Program A Lattice Cpld Programming' />CPLD Complex programmable logic devices. From DPEver get stuck choosing the right logic chip combination or voltage level translator Give up the hunt and create your own custom logic chip. CPLDs can give you the logic you need, with the pinout you want, while saving board space and board revisions. Development boards from Dangerous Prototypes will help you build your first custom logic chip using simple schematic entry, Verilog, or VHDL. XC9. 57. 2XL or XC2. C6. 4A CPLDs. On board power supply for core and pins. John, Thank you for the compliments. This article was written by Steve Chamberlin so he deserves the praise. A GAL could be configured to do as you sugest. Click on the device and choose program iMPACT will record the programming. CPLD families from Lattice and. Howto Programmable logic devices CPLD. How To Program A Lattice Cpld Programmer. Shop now for FPGA development boards, programming solutions, portable instrumentation and educational products. Jumper pins 6 individual pins, 0. Ideal for XILINX or other ports that may have a unique pin out for JTAG or SPI. IDC Cable 10 pin, 0. Ideal for JTAG or. CPLD Tutorial Learn Programmable Logic the. CPLD Tutorial Learn Programmable Logic the Easy. FPGA with the. Produces analog and digital FPGAs, including the ORCA FPSC assets purchased from Agere formerly Lucent. Ever get stuck choosing the right logic chip combination or voltage level translator Give up the hunt and create your own custom logic chip. CPLDs can give you the. The Systemyde 41CL takes advantage of modern technology to significantly add to the capabilities of the HewlettPackard 41C system. The 41CL circuit board replaces. Lattice Diamond and MachXO2 Breakout Board Tutorial. Programming the CPLD. Click the Program icon. LatticeSemi/Images/ProductImages/DesignSoftwareandIntellectualProperty/Diamond/featuresprojects.PNG?la=en&d=20140819T155457' alt='How To Program A Lattice Cpld Programming' title='How To Program A Lattice Cpld Programming' />Selectable 3. LEDs for output, push button for input. Easy to program with the Bus Pirate. Open source CC BY SA. Cool. Runner II and XC9. XL versions available for 1. JPG' alt='How To Program A Lattice Cpld Programming' title='How To Program A Lattice Cpld Programming' />Downloads. Hardware. XC9. 50. XLThe Xilinx XC9. XL family has some of the cheapest and readily available CPLDs out there. Inputs are 5volt tolerant and they can be run from a single 3. Utorrent Plus Crack Mac. Cool. Runner. IIThe Cool. Runner II family is newer than the XC9. XL, and has a few extra features like multiple IO voltage banks for voltage translation, internal pull up resistors and pin keepers and a clock divider. Requires a 1. 8volt core supply and a 1. IO pin supply. CPLD development tutorials. This tutorial shows how to use simple schematics to design the logic in a Xilinx Cool. Runner II or XC9. CPLD. Tutorial files. FPGA+Terms+FPGA+-+Field+Programmable+Gate+Array+SRAM+-+Static+RAM.jpg' alt='How To Program A Lattice Cpld Programming' title='How To Program A Lattice Cpld Programming' /> The Bus Pirate XSVF player and a. Modify the COM post and click to load. Schematic entry. Verilog. VHDLPlunify. Plunify is a cloud based compiler for Xilinx and Altera chips. The CPLD examples are already loaded, all you have to do is sign up for a free account and copy the tutorial from the add IP tab. Unfortunately it no longer supports Xilinx chips. ISE Webpack. Example devices. Schematic. VHDLVerilog. Programming. Additional methods. Links. Verilog. Resources. License. Hardware CC BY SA. CPLD demos projects CC 0.

The Bus Pirate XSVF player and a. Modify the COM post and click to load. Schematic entry. Verilog. VHDLPlunify. Plunify is a cloud based compiler for Xilinx and Altera chips. The CPLD examples are already loaded, all you have to do is sign up for a free account and copy the tutorial from the add IP tab. Unfortunately it no longer supports Xilinx chips. ISE Webpack. Example devices. Schematic. VHDLVerilog. Programming. Additional methods. Links. Verilog. Resources. License. Hardware CC BY SA. CPLD demos projects CC 0.